A Volume in the **Embedded Technology**™ Series

# Embedded Controller Hardware Design

by Ken Arnold

#### Embedded Control Hardware Design © 2001 by LLH Technology Publishing.

All rights reserved. No part of this book may be reproduced, in any form or by any means whatsoever, without permission in writing from the publisher. While every precaution has been taken in the preparation of this book, the publisher and author assume no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

ISBN: 1-878707-52-3

Library of Congress Control Number: 00-135391

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

Project management and developmental editing: Harry Helms, LLH Technology Publishing

Interior design and production services: Greg Calvert, Model, CO

Cover design: Sergio Villareal, Vista, CA

Technology Publishing

www.LLH-Publishing.com www.EmbeddedControllerHardwareDesign.com

#### **Dedication**

This book is dedicated in memory of my father, Kenneth Owen Arnold, who always encouraged me to follow my dreams. When other adults discouraged me from entering the engineering field, he told me, "If you really like what you're doing and you're good at it, you will be successful." Nowadays I get paid to have fun doing things I'd do for free anyway, so that meets my definition of success! Thanks, Dad.

#### Acknowledgment

This book is a direct result of contributions from many of the students I have been fortunate enough to have in my embedded computer engineering courses at the University of California—San Diego extension. They have provided a valuable form of feedback by sharing their notes and pointing out weaknesses in the text and in-class presentations. Some sections of this text were also provided by David Fern and Steven Tietsworth.

I would also like to thank my family for supporting me and, Mary, Nikki, Kenny, Daniel, Amy, and Annie for being patient and helping out when I needed it!

| 1 | Review of Electronics Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                            |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|   | Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                                                                                            |

|   | Embedded Microcomputer Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

|   | Microcomputer and Microcontroller Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                            |

|   | Digital Hardware Concepts  Voltage, Current, and Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                                                            |

|   | Voltage, Current, and Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                            |

|   | Diodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                                            |

|   | Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                                                                                            |

|   | Mechanical Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                           |

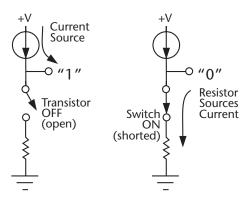

|   | Transistor Switch ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11                                                                                           |

|   | Transistor Switch OFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12                                                                                           |

|   | The FET as a Logic Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                                                                                           |

|   | NMOS Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13                                                                                           |

|   | CMOS Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                                                                           |

|   | Mixed MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                           |

|   | Real Transistors Don t Eat Q!                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16                                                                                           |

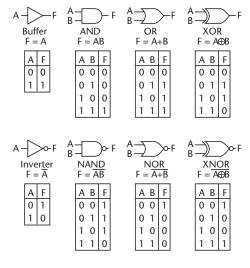

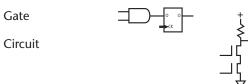

|   | Logic Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                                           |

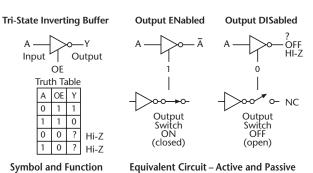

|   | Tri-State Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                           |

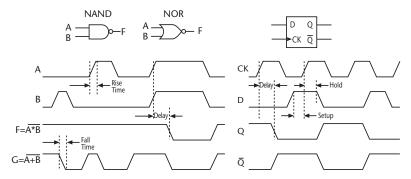

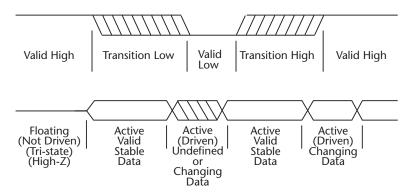

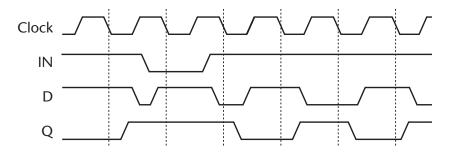

|   | Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                           |

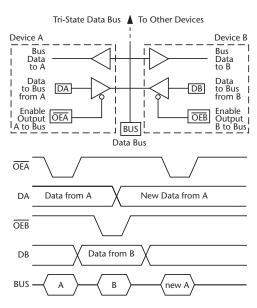

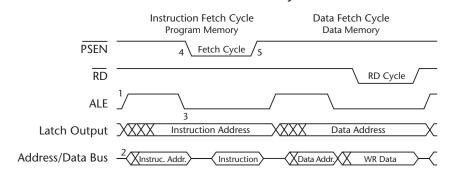

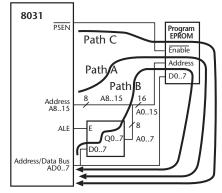

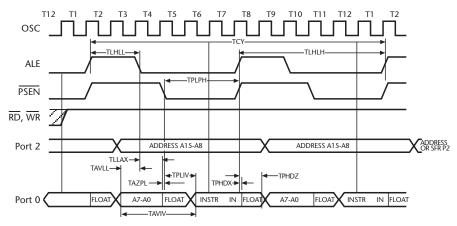

|   | Multiplayed Rus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                           |

|   | Multiplexed Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21                                                                                           |

|   | Loading and Noise Margin Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|   | The Design and Development Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21                                                                                           |

|   | Chapter Öne Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22                                                                                           |

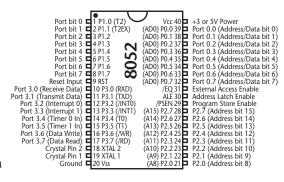

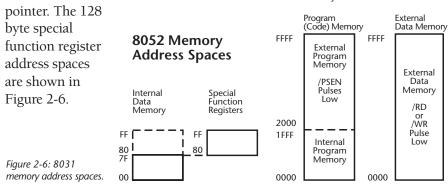

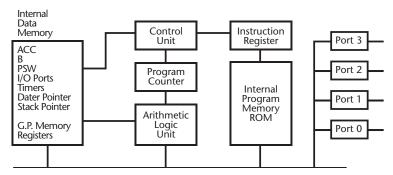

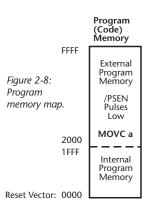

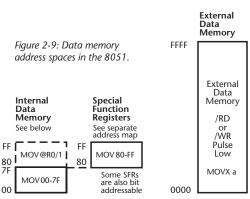

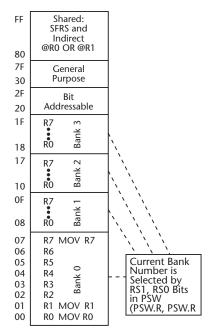

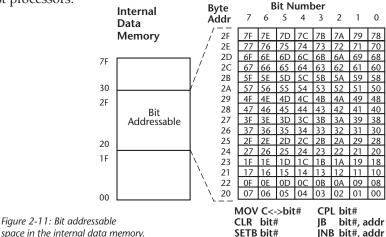

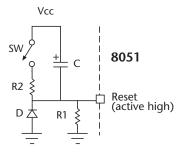

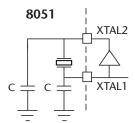

|   | Microcontroller Concepts Organization: von Neumann vs. Harvard Microprocessor/Microcontroller Basics Microcontroller CPU, Memory, and I/O Design Methodology The 8051 Family Microcontroller Processor Architecture Introduction to the 8051 Architecture Memory Organization CPU Hardware Oscillator and Timing Circuitry The 8051 Microcontroller Instruction Set Summary Direct and Register Addressing Indirect Addressing Indirect Addressing Generic Address Modes and Instruction Formats Address Modes The Software Development Cycle Software Development Tools Hardware Development Tools Chapter Two Problems | 24<br>24<br>25<br>26<br>27<br>28<br>30<br>32<br>41<br>42<br>43<br>50<br>51<br>55<br>55<br>56 |

|   | Onapter 1 WO F 100161113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                           |

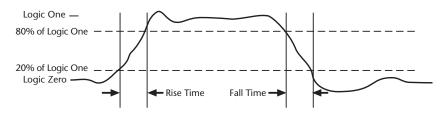

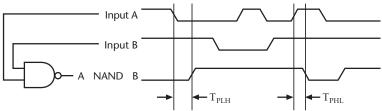

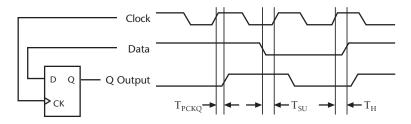

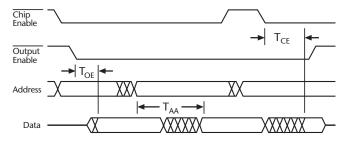

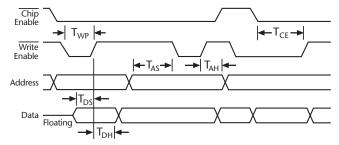

| 3 | Worst- Case Timing, Loading, Analysis, and Design Timing Diagram Notation Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>57</b> 58 59 59                                                                           |

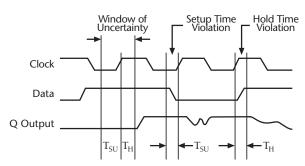

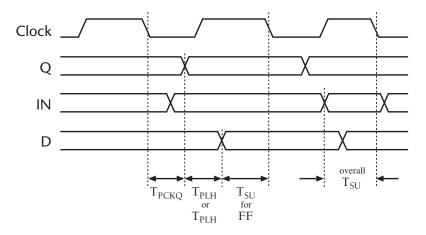

|   | Setup and Hold Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60                                                                                           |

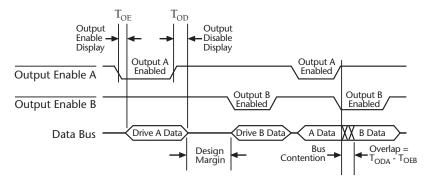

|   | Tri-State Bus Interfacing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                           |

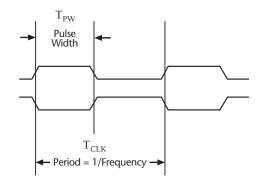

| Pulse Width and Clock Frequency                                                                   | 62  |

|---------------------------------------------------------------------------------------------------|-----|

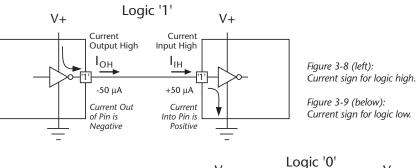

| Fan-Out and Loading Analysis DC and AC                                                            | 63  |

| Calculating Wiring Capacitance                                                                    | 66  |

| Fan-Out When CMOS Drives LSTTL                                                                    | 68  |

| Transmission Line Effects                                                                         | 70  |

| Ground Bounce                                                                                     | 72  |

| Logic Family IC Characteristics and Interfacing Interfacing TTL Compatible Signals to 5 Volt CMOS | 75  |

| Interfacing TTL Compatible Signals to 5 Volt CMOS                                                 | 78  |

| Design Example: Noise Margin Analysis Spreadsheet                                                 | 82  |

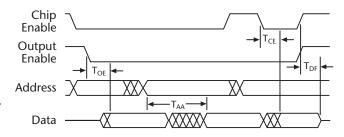

| Worst-Case Timing Analysis Example                                                                | 90  |

| Chapter Three Review Problems                                                                     | 92  |

|                                                                                                   |     |

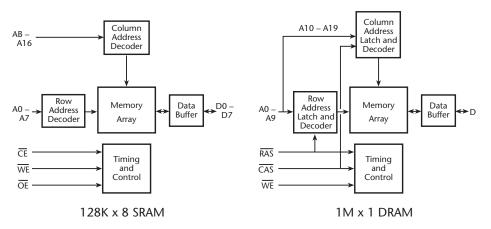

| 4 Memory Technologies and Interfacing                                                             | 95  |

| Memory Taxonomy                                                                                   | 96  |

| Secondary Memory                                                                                  | 97  |

| Volatility                                                                                        | 98  |

| Random Access Memory                                                                              | 98  |

| Sequential Access Memory                                                                          | 99  |

| Direct Access Memory                                                                              | 99  |

| Read/Write Memories                                                                               | 100 |

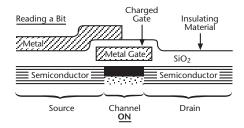

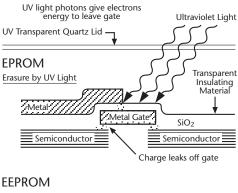

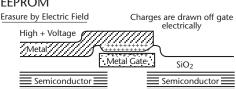

| Read-Only Memory                                                                                  | 101 |

| Other Memory Types                                                                                | 104 |

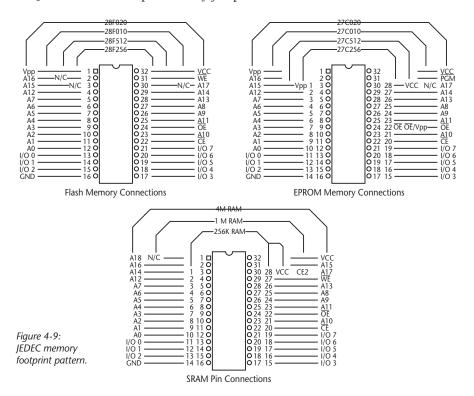

| JEDEC Memory Pin-Outs                                                                             | 105 |

| Device Programmers                                                                                | 106 |

| Memory Organization Considerations                                                                | 107 |

| Parametric Considerations                                                                         | 109 |

| Asynchronous vs. Synchronous Memory                                                               | 110 |

| Error Detection and Correction                                                                    | 111 |

| Error Sources                                                                                     | 111 |

| Confidence Checks                                                                                 | 111 |

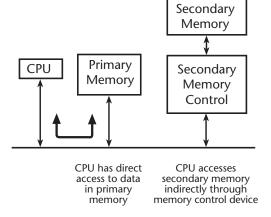

| Memory Management                                                                                 | 113 |

| Cache Memory                                                                                      | 114 |

| Virtual Memory                                                                                    | 114 |

| CPU Control Lines for Memory Interfacing                                                          | 115 |

| Chapter Four Problems                                                                             | 115 |

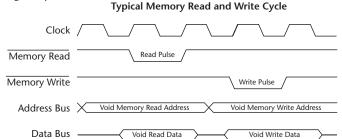

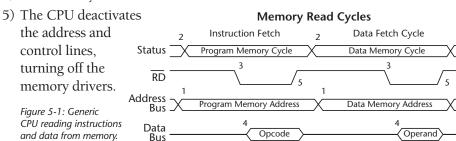

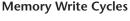

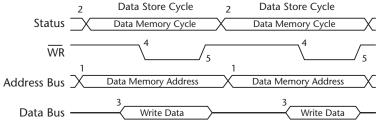

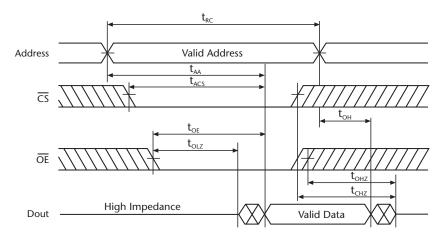

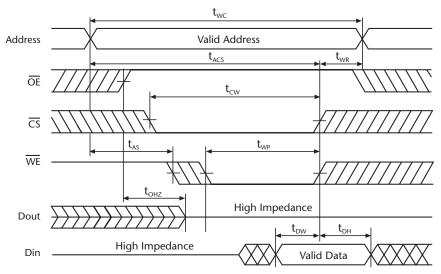

| Read and Write Operations                                                                         | 117 |

| redu and write operations                                                                         |     |

| 5 CPU Bus Interface and Timing                                                                    | 117 |

| Address, Data, and Control Buses                                                                  | 118 |

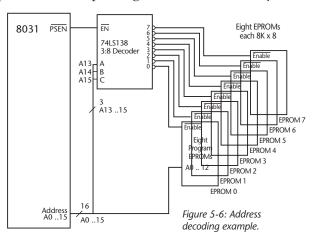

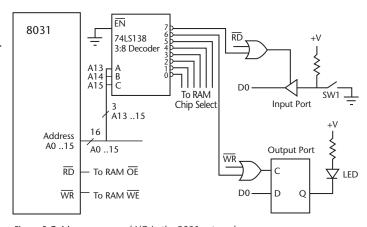

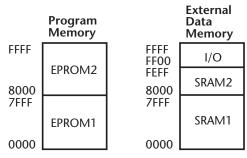

| Address Spaces and Decoding                                                                       | 120 |

| Address Map                                                                                       | 122 |

| Chapter Five Problems                                                                             | 124 |

| The Central Processing Unit (CPU)                                                                 | 125 |

| The Central Processing Offic (CPO)                                                                | 120 |

| 6 A Detailed Design Example                                                                       | 125 |

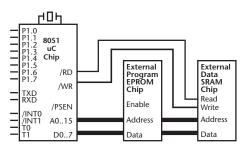

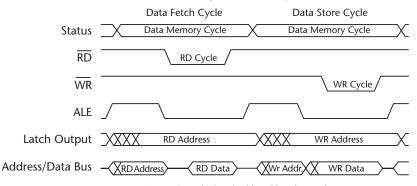

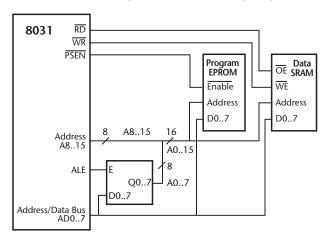

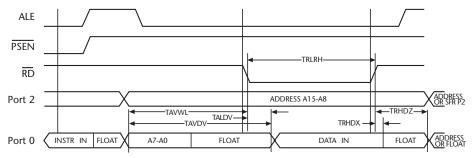

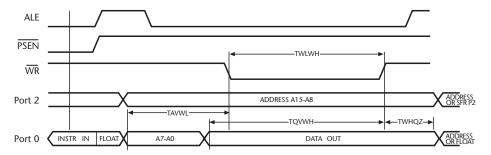

| External Data Memory Cycles                                                                       | 134 |

| External Memory Data Memory Read                                                                  | 134 |

| External Data Memory Write                                                                        | 134 |

| Design Problem 1                                                                                  | 138 |

| Design Problem 2                                                                                  | 139 |

| Design Problem 3                                                                                  | 140 |

| Design Fronting S                                                                                 | 140 |

| Completing the Analysis                                                                     | 142<br>143 |

|---------------------------------------------------------------------------------------------|------------|

| Memory Selection and Interfacing                                                            | 126        |

| Preliminary Timing Analysis                                                                 | 127        |

| 7 Programmable Logic Devices                                                                | 145        |

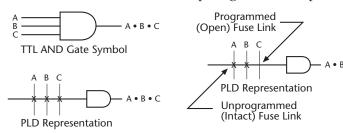

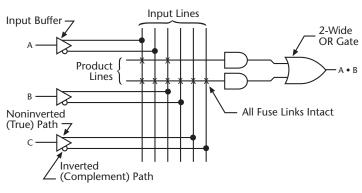

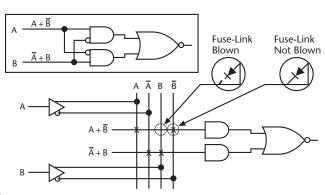

| Introduction to Programmable Logic                                                          | 147        |

| Introduction to Programmable Logic  Technologies: Fuse-Link, EPROM, EEPROM, and RAM Storage | 147        |

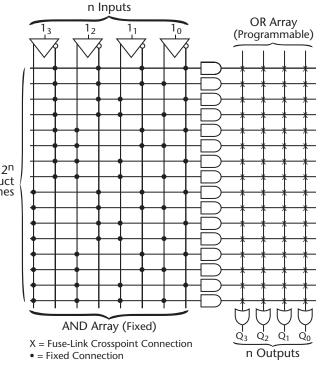

| PROM as PLD                                                                                 | 150        |

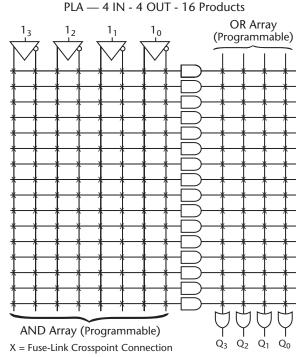

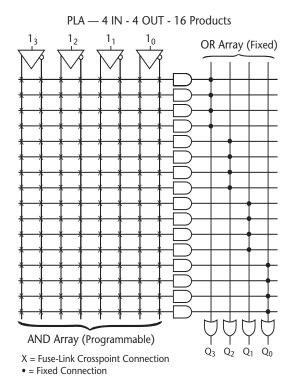

| Programmable Logic Arrays                                                                   | 151        |

| PAL-Style PLDs                                                                              | 151        |

| Design ExamplesPLD Development Tools                                                        | 153<br>155 |

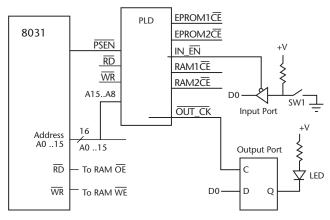

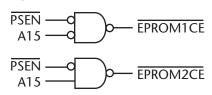

| Simple I/O Decoding and Interfacing Using PLDs                                              | 155        |

| IC Design Using PCs                                                                         | 157        |

| Chapter Seven Problems                                                                      | 157        |

| Direct CPU I/O Interfacing                                                                  | 161        |

| Billion of a fromtong                                                                       | 101        |

| 8 Basic I/ O Interfaces                                                                     | 161        |

| Port I/O for the 8051 Family                                                                | 161        |

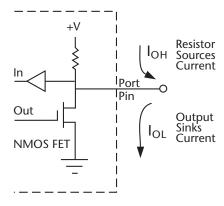

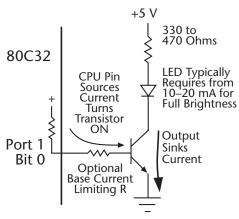

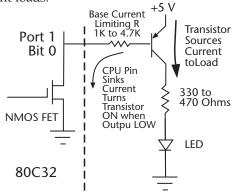

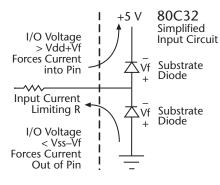

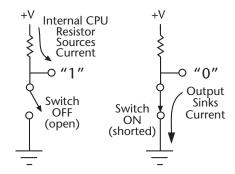

| Output Current Limitations                                                                  | 166        |

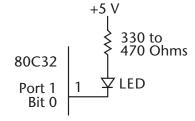

| Simple Input/Output Devices                                                                 | 169        |

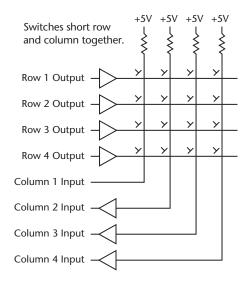

| Matrix Keyboard Input                                                                       | 170        |

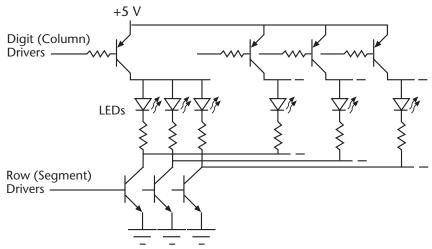

| Matrix Display Devices                                                                      | 171        |

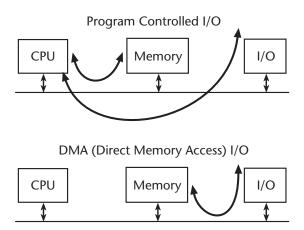

| Program-Controlled I/O Bus Interfacing                                                      | 173        |

| Real-Time Processing                                                                        | 175        |

| Direct Memory Access (DMA)                                                                  | 175        |

| Burst vs. Single Cycle DMA                                                                  | 176        |

| Cycle Stealing                                                                              | 177        |

| Elementary I/O Devices and Applications                                                     | 178        |

| Timing and Level Conversion Considerations Level Conversion                                 | 180<br>180 |

| Power Relays                                                                                | 180        |

| Chapter Eight Problems                                                                      | 181        |

|                                                                                             |            |

| 9 Other Interfaces and Bus Cycles                                                           | 183        |

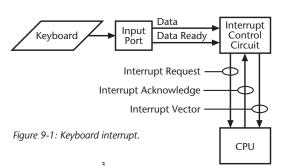

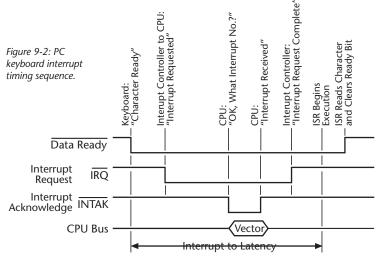

| Interrupt Cycles                                                                            | 184        |

| Software Interrupts                                                                         | 184        |

| Hardware Interrupts                                                                         | 184        |

| Interrupt Driven Program Elements                                                           | 186        |

| Critical Code Segments                                                                      | 187        |

| Semaphores                                                                                  | 188        |

| Interrupt Processing Options                                                                | 189        |

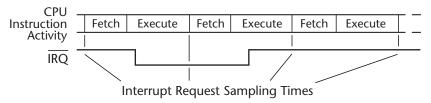

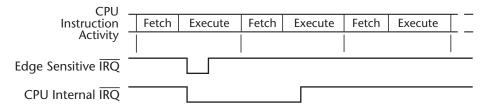

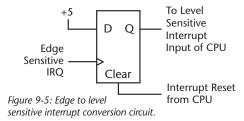

| Level and Edge Triggered Interrupts                                                         | 190        |

| Vectored Interrupts  Non-Vectored Interrupts                                                | 192<br>193 |

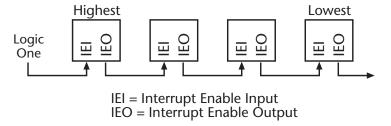

| Serial Interrupt Prioritization                                                             | 193        |

| Parallel Interrupt Prioritization                                                           | 194        |

| С                           | Construction Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 197                                                                                                        |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| E F:<br>H<br>SO<br>P        | Electromagnetic Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97<br>199<br>199<br>200<br>201<br>202<br>203<br>203<br>204<br>205<br>206                                   |

| Pow                         | er and Ground Planes 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 98                                                                                                         |

| Grou                        | und Problems 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98                                                                                                         |

| A<br>S<br>U<br>D            | Inalog Signal Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>09</b><br>210<br>211<br>211<br>212<br>215                                                               |

| D V C A V D C P A G P D E M | Define Power Supply Requirements Define Power Supply Required Supply | 15<br>216<br>217<br>218<br>218<br>219<br>220<br>220<br>222<br>222<br>222<br>222<br>222<br>222<br>222<br>22 |

| W<br>P                      | Veb and FTP Sites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>25</b><br>226<br>227<br>228<br>233                                                                      |

| Embedded Controller Hardware Design                  | 233 |

|------------------------------------------------------|-----|

| Controlling the World with Your PC                   | 233 |

| The Forrest Mims Engineers Notebook                  | 233 |

| The Forrest Mims Circuit Scrapbook, Volumes I and II | 233 |

| The Integrated Circuit Hobbyist s                    | 233 |

| Simple, Low-Cost Electronics Projects                | 233 |

#### **Preface**

During the early years of microprocessors, there were few engineers with education and experience in the applications of microprocessor technology. Now that microprocessors and microcontrollers have become pervasive in so many devices, the ability to use them has become almost a requirement for many technical people.

Today the microprocessor and the microcontroller have become two of the most powerful tools available to the scientist and engineer. Microcontrollers have been embedded in so many products that it is easy to overlook the fact that they greatly outnumber personal computers. Millions of PCs are shipped each year, but *billions* of microcontrollers ship annually. While a great deal of attention is given to personal computers, the vast majority of new designs are for embedded applications. For every PC designer, there are thousands of designers using microcontrollers in embedded applications. The number of embedded designs is growing quickly. The purpose of this book is to give the reader the basic design and analysis skills to design reliable microcontroller or microprocessor based systems. The emphasis in this book is on the practical aspects of interfacing the processor to memory and I/O devices, and the basics of interfacing such a device to the outside world.

A major goal of this book is to show how to make devices that are inherently reliable by design. While a lot of attention has been given to "quality improvement," the majority of the emphasis has been placed on the processes that occur *after* the design of a product is complete. Design deficiencies are a significant problem, and can be exceedingly difficult to identify in the field. These types of quality problems can be addressed in the design phase with relatively little effort, and with far less expense than will be incurred later in the process. Unfortunately, there are many hardware designers and organizations that, for various reasons, do not understand the significance and expense of an unreliable design. The design methodology presented in this text is intended to address this problem.

Learning to design and develop a microcontroller system without any practical hands-on experience is a bit like trying to learn to ride a bike from reading book. Thus, another goal is to provide a practical example of a complete working product. What appears easy on paper may prove extremely difficult without some real world experience and some potentially painful crashes. In order to do it right, it's best to examine and use a real design. On the other hand, the current state of the technology (surface mounted packaging, etc.) can make the practical side problematic. In order to address this problem, a special educational System Development Kit is available to accompany this book (8031SDK). All the documentation to construct an SDK is available on the companion CD-ROM. This info, along with updated information and application examples, is also available on the web site for this book: http://www.hte.com/echdbook. All the information needed to build the SDK is available there, as well as information on how to order the SDK assembled and tested.

While searching for an appropriate text for one of the courses I teach in embedded computer engineering, I was unable to locate a book that covered the topic adequately. An earlier version of this book was written to accompany that course and has since evolved into what you see here. The course is offered at the University of California, San Diego Extended Studies, and is titled "Embedded Controller Hardware Design." The same courses may also be taken in an on-line format using the Internet, and can be found at http://www.hte.com/uconline/ecd The goals of the course and the book are very much the same: to describe the *right way* to design embedded systems.

While no prior knowledge of microcontrollers or microprocessors is required, the reader should already be familiar with basic electronics, logic, and basic computer organization. Chapter one is intended as a review of those basic concepts. Next there is a general overview of microcontroller architecture, and a specific microcontroller chip architecture, the 8051 family, is introduced

and detailed. The 8051 was chosen because it can be interfaced to external memory, has simple timing specs, is widely used and available from a number of manufacturers. The concepts of worst-case design and analysis are described, along with techniques for hardware interfacing. A good embedded design requires familiarity with the underlying memory technology, including ROM, SRAM, EPROM, Flash EPROM, EEPROM storage mechanisms and devices. The processor bus interface is then covered in general form, along with an introduction to the 8051's bus interface. Most embedded designs can also benefit from the use of user programmable logic devices (PLD). This subject is too complex for in-depth coverage here, so PLD technology is covered from a relatively high level. The central theme of designing an embedded system that can be proven to be reliable is illustrated with a simple embedded controller. The iterative nature of the design process is shown by example, and several design alternatives are evaluated. With the central part of the design completed, the remaining chapters cover the various types of I/O interfaces, bus operations, and a collection of information that is seldom included in the usual sources, but is often handed down from one engineer to another.

I hope that you will find this book to be useful, and welcome any observations and contributions you may have. If you should find any errors in the text, or if you know of some good embedded design resources, please feel free to contact me directly by e-mail: ken.arnold@ieee.org

# Review of Electronics Fundamentals

Why are microprocessors and microcontrollers designed into so many different devices? While there are many dry and practical reasons, I suspect one of the strongest motivations for using a microprocessor is simply that it is a lot more fun.

Over the past few decades of the so-called "computer revolution," I have seen many products and projects that could have been handled without resorting to a microprocessor. Yet there is always a tendency to rationalize the choice of a micro-based solution by economic or technical arguments to support the decision. In fact, most of the really excellent products were successful to a great extent because they were fun to develop. Many of the best product ideas have occurred when someone was "playing" with something they were interested in. In my own experience, I have found learning something new is much easier and more effective when I am "just playing around" rather than trying to learn in a structured way or against a deadline. Studies of various educational methods also indicate "coached exploration" is more effective than the traditional methods. These and other observations lead me to the conclusion that the best way to learn about a microcontroller is by "playing" with one.

No book—no matter how well written—can possibly motivate and educate you as well as building and playing with a microcontroller. The best way to learn the concepts in this book is to build a simple microcontroller. Even if it is capable of nothing more than blinking a light, it will provide a concrete example of the microcontroller as a tool that can be fun to use. To ease this effort, a companion system development kit (SDK), is available to accompany this text. It incorporates the functions of a stand-alone single board computer (SBC), and an in-circuit emulator (ICE). It also serves as a sample embedded controller design. The design is included on the CD-ROM and web site for this book, so anyone can reproduce and use it as a learning tool. By applying

the guidelines set forth in this book to real world hardware, you can learn to design reliable embedded hardware into other products. Information on obtaining the SDK can be found in the Preface.

# **Objectives**

Several different skills are required for successful embedded hardware design. Here are some of the things you will know how to do when you finish this book:

- Interpret design requirements for the design of an embedded controller.

- Read and understand the manufacturer's specification sheet.

- Select appropriate ICs for the design.

- Interface the CPU, memory, and I/O devices to a common bus.

- Design simple I/O (input/output) interfaces.

- Define the decoding and interconnection of the major components.

- Perform a worst-case analysis of the timing and loading of all signals.

- Understand the software development cycle for a microcontroller.

- Debug and test the hardware and software designs.

These tasks represent the major skills required in the successful application of an embedded micro. In addition, other abilities—such as the design and implementation of simple user programmable logic—will be covered as required to support the proficient application of the technology.

# **Embedded Microcomputer Applications**

There is an incredible diversity of applications for embedded processors. Most people are aware of the highly visible applications, but there are many less apparent uses. Many of the projects my students have chosen turned out to be of practical use in their work. However, they have covered the entire range from the economically practical to the blatantly absurd. One practical example was the use of a microprocessor to monitor and control the ratio of ingredients used in mixing concrete. About a year after the student implemented the system, he wrote to inform me that the system had saved his company between two and three million dollars a year by reducing the number

of "bad batches" of concrete that had to be jack hammered out and replaced. Another example was that of a student who suspended a ball by airflow generated by a fan and provided closed loop control of the ball's position with the microprocessor. The only thing that many of the student projects really had in common was the use of a microcontroller as a tool.

Some of the actual commercial applications of embedded computer controls that the author has been directly involved with include:

- A belt measures a person's heart rate and respiration that signals an alarm

when safe limits are exceeded. A radio signal is then transmitted to a

microcontroller in a pocket pager to display the type of problem and the

identity of the belt.

- An environmental system controls the heating ventilating and air conditioning in one or more large buildings to minimize peak energy demands.

- A system that measures and controls the process of etching away the unwanted portions of material from the surface of an integrated circuit being manufactured.

- The fare collection system used to monitor and control entry to a rapid transit system based on the account balance stored on the magnetic stripe on a card.

- Determination of exact geographic position on the earth by measuring the time of arrival of radio signals received from navigational beacons.

- An intelligent phone that receives radio signals from smoke alarms, intrusion sensors, and panic switches to alert a central monitoring station to potential emergency situations.

- A fuel control system that monitors and controls the flow of fuel to a turbine jet engine.

Selecting a particular processor for a given application is usually a function of the designer's familiarity with a particular architecture. While there are many variations in the details and specific features, there are two general categories of devices: microprocessors and microcontrollers. The key difference between a *microprocessor* and a *microcontroller* is that a microprocessor contains only a central processing unit (CPU) while a microcontroller has memory and I/O on the chip in addition to a CPU. Microcontrollers are generally used for dedicated tasks. *Microcomputer* is a general term that applies to complete computer systems implemented with either a microprocessor or microcontroller.

# Microcomputer and Microcontroller Architectures

Microprocessors are generally utilized for relatively high performance applications where cost and size are not critical selection criteria. Because microprocessor chips have their entire function dedicated to the CPU and thus have room for more circuitry to increase execution speed, they can achieve very high-levels of processing power. However, microprocessors require external memory and I/O hardware. Microprocessor chips are used in desktop PCs and workstations where software compatibility, performance, generality, and flexibility are important.

By contrast, microcontroller chips are usually designed to minimize the total chip count and cost by incorporating memory and I/O on the chip. They are often "application specialized" at the expense of flexibility. In some cases, the microcontroller has enough resources on-chip that it is the only IC required for a product. Examples of a single-chip application include the key fob used to arm a security system, a toaster, or hand-held games. The hardware interfaces of both devices have much in common, and those of the microcontrollers are generally a simplified subset of the microprocessor. The primary design goals for each type of chip can be summarized this way:

- microprocessors are most flexible

- microcontrollers are most compact

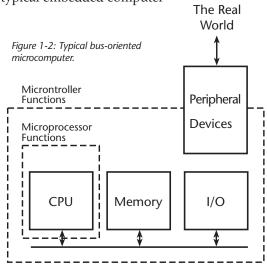

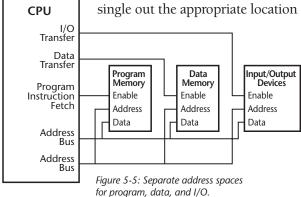

There are also differences in the basic CPU architectures used, and these tend to reflect the application. Microprocessor based machines usually have a *von Neumann architecture* with a single memory for both programs and data to allow maximum flexibility in allocation of memory. Microcontroller chips, on the other hand, frequently embody the *Harvard architecture*, which has separate memories for programs and data. Figure 1-1 illustrates this difference.

Figure 1-1: At left is the von Neumann architecture; at right is the Harvard architecture.

One advantage the Harvard architecture has for embedded applications is due to the two types of memory used in embedded systems. A fixed program and constants can be stored in non-volatile ROM memory while working variable data storage can reside in volatile RAM. Volatile memory loses its contents when power is removed, but non-volatile ROM memory always maintains its contents even after power is removed.

The Harvard architecture also has the potential advantage of a separate interface allowing twice the memory transfer rate by allowing instruction fetches to occur in parallel with data transfers. Unfortunately, in most Harvard architecture machines, the memory is connected to the CPU using a bus that limits the parallelism to a single bus. A typical embedded computer

consists of the CPU, memory, and I/O. They are most often connected by means of a shared bus for communication, as shown in Figure 1-2.

The peripherals on a microcontroller chip are typically timers, counters, serial or parallel data ports, and analog-to-digital and digital-to-analog converters that are integrated directly on the chip. The performance of these peripherals is generally less than that of dedicated peripheral chips, which are

frequently used with microprocessor chips. However, having the bus connections, CPU, memory, and I/O functions on one chip has several advantages:

- Fewer chips are required since most functions are already present on the processor chip.

- Lower cost and smaller size result from a simpler design.

- Lower power requirements because on-chip power requirements are much smaller than external loads.

- Fewer external connections are required because most are made on-chip, and most of the chip connections can be used for I/O.

- More pins on the chip are available for user I/O since they aren't needed for the bus.

- Overall reliability is higher since there are fewer components and interconnections.

Of course there are disadvantages too, including:

- Reduced flexibility since you can't easily change the functions designed into the chip.

- Expansion of memory or I/O is limited or impossible.

- Limited data transfer rates due to practical size and speed limits for a single-chip.

- Lower performance I/O because of design compromises to fit everything on one chip.

# **Digital Hardware Concepts**

In addition to the CPU, memory, and I/O building blocks, other logic circuits may also be required. Such logic circuits are frequently referred to as *glue logic* because they are used to connect the various building blocks together. The most difficult and important task the hardware designer faces is the proper selection and specification of this "glue logic." Devices such as registers, buffers, drivers and decoders are frequently used to adapt the control signals provided by the CPU to those of the other devices. While TTL gate level logic is still in use for this purpose, the *programmable logic device* (PLD) has become an important device in connecting the building blocks. Contemporary microcontroller designers need to acquire the following skills:

- Interpretation of manufacturers specifications

- Detailed, worst case timing analysis and design

- Worst case signal loading analysis

- Design of appropriate signal and level conversion circuits

- Component evaluation and selection

- Programmable logic device selection and design

The glue logic used to join the processor, memories, and I/O is ultimately composed of logic gates, which are themselves composed almost entirely of transistors, diodes, resistors, and interconnecting wires. In order to understand the basic operation of the glue logic, we are going to begin at the component level with a review of basic electronics concepts. These concepts will be presented as fluid flow analogies.

# Voltage, Current, and Resistance

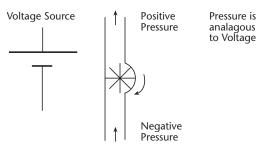

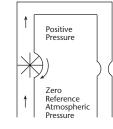

In Figure 1-3, a battery provides a voltage source for electricity, much like a pump provides a pressure source for a fluid. Voltage, or pressure, is required to produce current flow in the circuit.

The voltage source provides the pressure "motivation," if you will, for current flow. Resistance provides a limiting constraint on the

Figure 1-3: Voltage in an electrical circuit is analogous to pressure in a fluid.

amount of current that will actually flow. The resistor will allow a current to flow through it that is proportional to the voltage across it, and inversely proportional to the resistance value. Higher resistance is like a smaller aperture

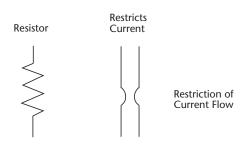

for the fluid to flow through. The resistance results in a voltage, or pressure drop, across the resistance as long as current is flowing in the resistor. Figure 1-4 illustrates this.

The wiring connecting the components in a circuit is like the piping connecting plumbing components that let a fluid flow. The flow of current in the circuit

Figure 1-4: Resistance in an electrical circuit is analogous to a restriction in the flow of a fluid.

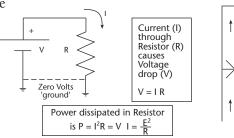

is controlled by the magnitude of the voltage (pressure) and the resistance (pressure drop) in the circuit. In Figure 1-5, the battery provides a voltage to force current through the resistor. The magnitude of the voltage (V) generated by the battery is developed across the resistor, and the magnitude of the resistance (R), determine the current (I). Note the "return" current path is often shown as "ground," which is the reference voltage used as the "zero volts" point. In this case, current flows from the positive battery terminal, through the wire, then the resistor, then through the "ground" connection to the minus terminal of the battery. This is usually not the same as earth ground, which provides a connection to a stake or pipe literally stuck in the ground. The magnitude of the current in this case is I = V / R by re-arranging the

8

equation V = I \* R, as shown in Figure 1-5. This is known as Ohm's law. Another way to look at it is that whenever current flows through a resistor,

there is a drop in voltage across the resistor due to the restriction — in current.

Real components are not the perfect voltage sources, resistances, etc. we have discussed so far. They have parasitic values that limit

Figure 1-5: Voltage across R is equal to current multiplied by resistance.

their performance in the real world and are subject to other limitations, such as operating temperature, power limits, etc. Current flows only through a complete circuit, and in most cases (for a positive power supply) current flows from the power source through the circuitry and returns to the power supply through the common "ground" connection. Current flowing through any resistance results in the dissipation of power as heat. The power dissipated is  $P = I^2R = V^*I = V^2/R$ . Note that voltage is sometimes denoted by the variable V and sometimes by E, for *electromotive force*.

All practical components have some resistance. Real batteries have an internal resistance, for example, which provides an upper limit to the current the battery can supply to an external circuit. Real wires have resistance as well, so the actual performance of a circuit will deviate somewhat from the ideal. These effects are obvious in some cases, but not in others. In an automobile starting circuit, it's not surprising that the battery, supplying 12 volts to a starter with internal resistance on the order of 0.01 to 0.1 ohms, will result in currents of hundreds of amperes in order to start the engine. On the other hand, while consulting with a prominent notebook computer manufacturer, I uncovered a design error resulting in an internal current of hundreds of amperes flowing in the circuit for a few nanoseconds. Obviously, this wreaked havoc on the operation of the computer, and generated a great deal of electromagnetic noise!

One of the things you will learn in this book is how to avoid those kinds of mistakes. It's also important to remember that power is dissipated in *any* resistance present in the circuit. The power is proportional to the voltage times

the current across the resistance, which is dissipating the power. In the last two examples, the amount of power dissipated instantaneously is quite high while the current is flowing. When the current pulse is only a few nanoseconds long, however, it may not be

obvious, since there won't be much heat generated.

# Current Diode is analgous to a one-way valve. Current can only flow in one direction.

#### **Diodes**

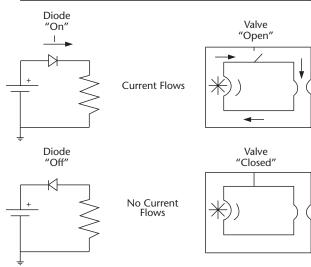

The diode is a simple semiconductor device acting as a "one way" current valve. It only lets current flow in one direction. Figure 1-6 illustrates how the diode operates like a "one-way" fluid valve.

(Purists please note: This book does not use electron current flow. All electrical current flow will be "positive" or "conventional" current flow, meaning current

Figure 1-6: A diode to electricity is analogous to a valve in the flow of a fluid.

always flows from the most positive terminal to the most negative terminal of a component. The use of positive current flow follows the intuitive direction of the arrows inherent in the component drawings for diodes, transistors, etc.)

#### **Transistors**

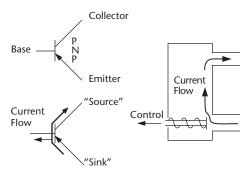

The flow analogy can also be used to model how a transistor operates in a logic circuit. The transistor is an amplifier. It uses a small amount of energy to control a larger energy source, just as a valve controls a high-pressure water source. There are two kinds of transistors: *bipolar* and *field-effect transistors* (FETs). We will look at bipolar transistors first; these amplify current. A small amount

of current flows in the control circuit (the transistor base-emitter circuit) to turn the transistor on. This control current is amplified (multiplied by the gain or *beta* of the transistor) and allows a larger current to flow in the output circuit (the collector-emitter circuit). Once again, the device is not perfect because of the resistance, current, gain, and

Figure 1-7: Operation of a bipolar PNP transistor.

leakage limitations of real transistors. Bipolar transistors come in two polarities, NPN and PNP, with the difference being the direction in which current

flows for normal operation. A bipolar PNP transistor is shown and modeled in Figure 1-7.

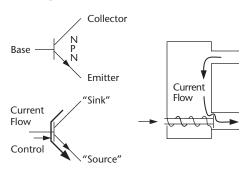

For most of the illustrative circuit examples in this book, we will be using NPN transistors, as shown in Figure 1-8.

#### **Mechanical Switches**

Figure 1-8: Operation of a bipolar NPN transistor.

Mechanical switches are useful for direct input to digital circuits. One of the more convenient versions is a bank of rocker switches packaged into a module that can fit into the same location as a standard chip. The *dual in-line package*, or DIP, switch is one of the easiest ways to add multiple switches to a microcontroller design. The mechanical switch has extremely low "on" resistance and high "off" resistance, unlike most semiconductor switches. Figure 1-9 shows a typical DIP switch and the schematic symbol for it.

Figure 1-9: 8-position DIP switch and schematic equivalent.

# Transistor Switch ON

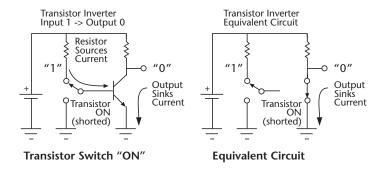

Transistors can be configured to function as switches. As can be seen in Figure 1-10, an NPN transistor operating as a current controlled switch can be used to build a simple inverter. It changes a logic one on its input to a logic zero at its output, and vice versa. In this case, logic one is represented as a positive voltage, and a logic zero is represented by zero volts. The logic one input (positive input voltage) is supplied through a resistor from the power supply voltage to the transistor base terminal, resulting in a small base control current into the base.

Figure 1-10: The transistor inverter; input = 1 and transistor ON. The transistor ON configuration is at left and the equivalent circuit is at right.

The transistor is used because it has gain allowing a larger output current to flow as controlled by a weaker input. When the transistor is turned on as much as it can be, the collector emitter circuit looks almost like a short circuit, effectively connecting the output to ground or zero volts. This gives a logic zero on the collector output. When the transistor collector is shorted to ground, current flows from the supply through the resistor and into the transistor collector to ground. The transistor is said to *sink* the resistor current into ground. If there is an external load, such as another inverter or gate, connected to the collector output, the transistor can also sink current from the load. This is also referred to as *pulling down* the output voltage. The current sinking capacity of the transistor limits the number of devices this inverter can drive.

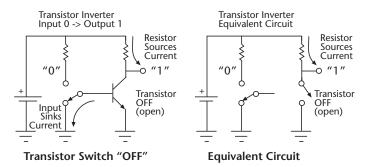

#### **Transistor Switch OFF**

When the input is connected to logic zero (ground voltage), no current flows into the base of the transistor, since its base and emitter terminals are at the same voltage. When there is no current flowing in the base, the transistor will not allow current to flow in the collector emitter circuit either. As a result, the circuit behaves as if the transistor was removed from the circuit. The output resistor will source current to any potential load. The output is pulled up to the supply voltage, resulting in a logic one at the output. Once again, there is a limit to the resistor's ability to source current, resulting in a limit to the number of loads that can be attached to this circuit's output. Notice these two limits are defined by the ability of the transistor to pull down the output, and the resistor's ability to pull up the output become the main limits to its ability to drive other devices. Gates can be constructed by adding diodes or transistors to the inverter circuit in Figure 1-11.

Figure 1-11: The transistor inverter; input = 0 and transistor OFF.

The transistor OFF configuration is at left and the equivalent circuit is at right.

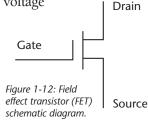

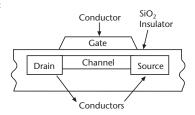

#### The FET as a Logic Switch

Most of the logic devices used in highly integrated circuits do not use bipolar transistors. Instead, they use field effect transistors. FETs perform a similar function to the bipolar transistors discussed earlier, but they are voltage

controlled. While the current flowing in the base controls bipolar transistors, the voltage between the gate and source controls field effect transistors. The gate voltage of a field effect transistor controls the current flowing in the drain-source circuit. The symbol for the FET shows the gate to be insulated from the source-drain circuit, as shown in Figure 1-12.

13

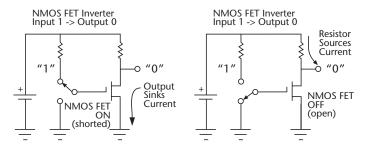

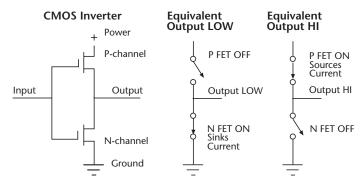

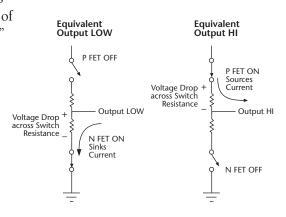

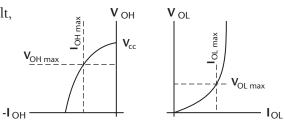

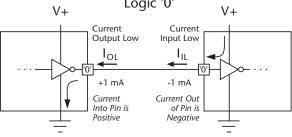

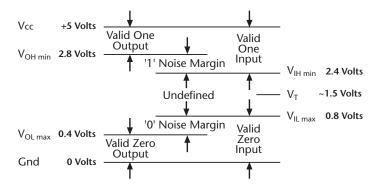

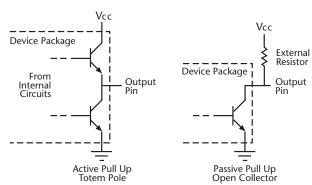

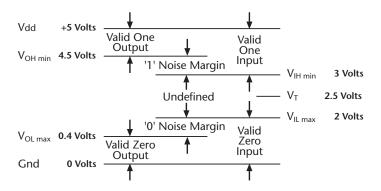

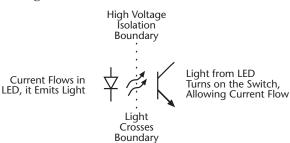

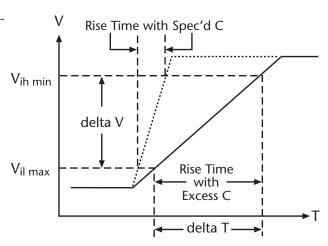

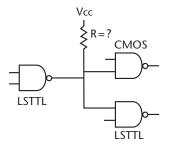

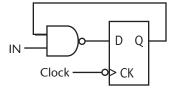

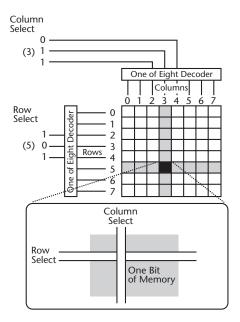

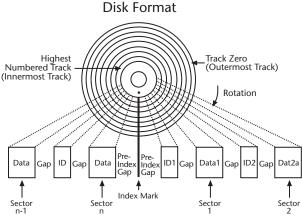

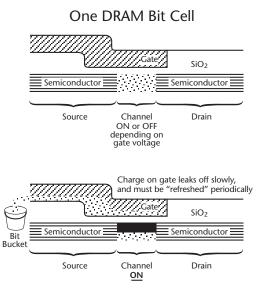

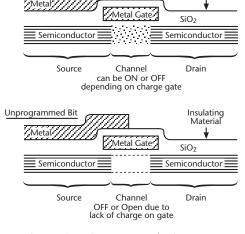

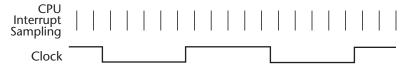

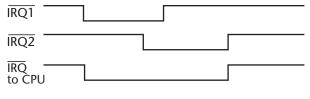

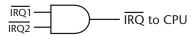

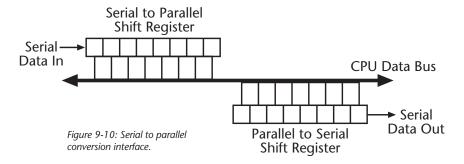

This type of FET is referred to as a MOSFET ( $metal\ oxide\ semiconductor\ FET$ ), since the insulating material is silicon dioxide ( $SiO_2$ ), commonly known as